Embedded systems require fast response to exceptions and interrupt handlers. In this paper, the characteristics of exception handling under ARM architecture are analyzed, and an efficient exception handling solution based on ARM processor is proposed. Based on LPC3250 hardware platform, the scheme is designed and implemented. The test results show that the exception handling of this scheme is more efficient.

In the fields of aerospace, industrial control and medical, the security, reliability and efficiency of embedded systems play a significant role, while anomalies are emergencies in the process of operation. Whether the exception handling is efficient will directly affect the whole system. Work efficiency. In order to ensure the efficient and safe operation of the embedded system, it is of great significance to study the efficient exception handling mechanism in the abnormal mode of the processor.

1 Exception overview

An exception/interrupt in an embedded system is an event that is generated by an internal or external source of the processor and causes the system to process it. According to the different event sources, the exception is divided into two types: "exception" and "interrupt". The exception refers to events caused by the internal source of the processor, such as illegal instruction execution exception, address access exception, etc.; interrupt refers to the external interrupt source by the processor. The incident caused. The embedded processor to the external interrupt source is generally managed by the interrupt controller and reported to the processor. For embedded systems, exceptions/interrupts cause the processor to interrupt the normal program execution flow and enter a specific mode for corresponding exception handling. Therefore, there is generally no strict distinction between "abnormal" and "interruption".

As an embedded processor, the ARM processor supports a complete exception handling mechanism to ensure the real-time performance of the system and the stability of program execution. There are 7 types of exceptions in the ARM processor. Each exception has its own fixed exception vector address. After the exception is generated, the processor will switch to the corresponding abort mode. The specific description is shown in Table 1.

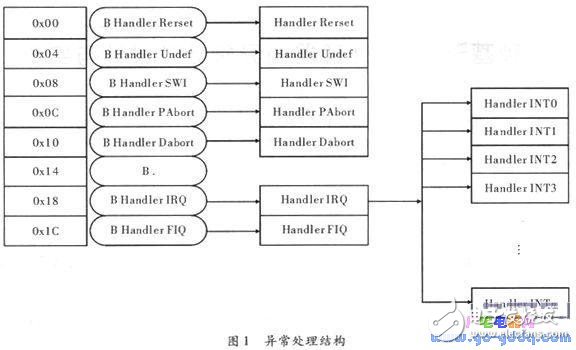

ARM supports multiple interrupt nesting, so each exception has a fixed priority, in order: reset, data abort, FIQ, IRQ, prefetch abort, undefined instruction, and SWI. There is only 4 bits of space between each exception vector, so only jump instructions can be placed in the vector table. Usually the exception handling structure is shown in Figure 1.

2 abnormal response and return process

2.1 Abnormal response

When any of the 7 exceptions occurs with the response allowed, the processor performs the necessary preprocessing as follows:

(1) The Prec Program Status Register (CPSR) is in the Saved Program Status Registrar (SPSR) corresponding to each exception.

(2) The control bit in the PSR causes the processor to enter the corresponding abnormal interrupt mode. At the same time, the program status is ARM state, and the IRQ interrupt is disabled. If the abnormal response is a reset exception or FIQ abnormality, the FIQ interrupt is also prohibited.

(3) Return the address and save it to the corresponding LR register.

(4) Enter the address into the PC, jump and execute the interrupt service routine.

2.2 Abnormal return

The exception return is executed after the exception service routine is completed. The kernel needs the user to complete the following return actions: (1) The contents of the PSR register are returned to the CPSR register. (2) The value of the R register is assigned to the PC. (3) When the interrupt service routine is entered, the values ​​of some general-purpose registers are saved. At this time, the values ​​of these saved general-purpose registers need to be restored, and the interrupt disable bit is cleared.

3 design of exception service program

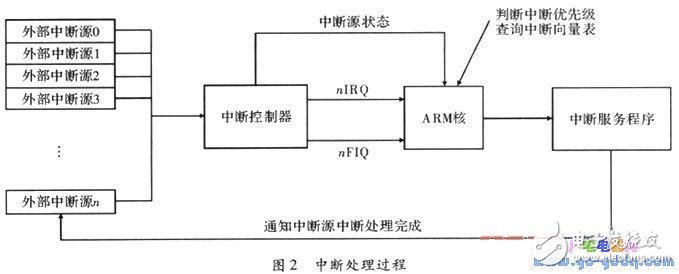

The LPC3250 hardware platform integrates two levels of interrupt control on the board and supports a total of 74 interrupt sources. One level of interrupt controller can receive 32 external interrupt requests, all interrupts notify the ARM core through FIQ or IRQ interrupt signals, so the interrupt controller needs to manage all external interrupt sources.

In the interrupt controller, the ATR (AcTIvaTIon Type Register) register is used to set the trigger mode of the interrupt. The external interrupt supports the edge trigger and level trigger. The APR (AcTIvaTIon Polarity Register) register is used to determine the interrupt type and supports the high potential active and low potential. The ITR (Interrupt Type Register) register is used to set the interrupt mode, including FIQ and IRQ. The response speed and priority of FIQ are higher than IRQ, support data transmission or channel processing, and reduce the occupation by using unique registers. Registers, usually embedded systems use IRQ abort mode management for all external interrupts; IER (InterruptEnable Register) registers are used to mask or enable external interrupts; RSR (Raw Stat us Register) registers are used to describe all current interrupt source states. .

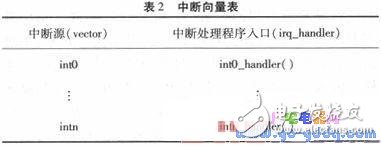

When the interrupt source generates an interrupt, the processor executes the processing routine from the IRQ or FIQ exception entry. Generally, the embedded system has different interrupt service programs according to the difference of the interrupt source. In order to correctly determine the specific interrupt source, the system maintains the interrupt vector table of the associated interrupt controller in addition to the exception vector table. The structure is shown in Table 2. .

The interrupt vector table is used to store the entry address of the interrupt service program corresponding to the specific interrupt source. When responding to a peripheral interrupt request, the interrupt service routine is recognized by the interrupt controller and the processing routine is executed according to the interrupt vector table.

The LPC3250 platform is designed to not prioritize the interrupt source through the interrupt controller. After the interrupt source status is obtained through the RSR register, the system software performs the interrupt source priority configuration. In the interrupt processing, the system selects the current highest priority interrupt and enters the interrupt processing routine corresponding to the interrupt source. The interrupt processing process is shown in Figure 2.

4 implementation of exception service program

Round Hole Breadboard,Solderless Breadboard Connections,Tie Point Breadboard,Solderless Prototype Breadboard

Cixi Zhongyi Electronics Factory , https://www.zybreadboard.com