Both wireless systems and cable system designers must pay attention to power efficiency issues, although the starting point for both parties is different: for mobile devices, longer battery life, longer talk time, or longer working hours are noticeable. Advantages, lower power requirements mean using smaller batteries or choosing different battery technologies, which also alleviates battery heating to a certain extent; for wired systems, designers can reduce power supply size and reduce cooling requirements And reduce fan noise to improve battery efficiency. Rarely mention the fact that improving power efficiency can also save space, and the space saved can be used to add components that can improve system performance, especially when the design team wants to add more than one processor.

When designing an embedded DSP processor or system with a demanding power system, DSP-specific technology, operating system and its supporting software can reduce power consumption. DSP or dual processor designs that go beyond traditional technology excel in saving energy.

Power consumption basics

The total power consumption of a complementary metal oxide semiconductor (CMOS) circuit is the sum of dynamic power and static power:

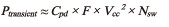

Dynamic power dissipation occurs when a logic state transition occurs in the gate and a switching current is required to charge the internal node and a P-channel and N-channel transient turn-on causes a shoot-through current. The approximate value can be estimated by the following formula:

Among them, Cpd is the dynamic capacitance, F is the switching frequency, Vcc is the power supply voltage, and Nsw is the number of converted bits. In addition, the voltage (Vcc) determines the maximum switching frequency (F) under steady state operation. The above relationship contains two important concepts: dynamic power consumption is linear with the switching frequency and has a quadratic relationship with the supply voltage; the maximum safe switching frequency depends on the supply voltage. For the purposes of this discussion, a particular frequency and voltage pair is referred to as a "set point."

Obviously, lowering the CPU clock rate will proportionally reduce the dynamic power consumption. Since the dynamic power consumption is quadratic with the power supply voltage, the power consumption can be greatly reduced by lowering the voltage without affecting the system performance. However, for a particular set of tasks, lowering the CPU clock rate will also proportionally extend the time it takes to execute the task set, so the application must be carefully analyzed to ensure that its real-time requirements are met.

Static power consumption is mainly due to transistor leakage current. In general, the static power consumption of CMOS circuits is very low, which is negligible compared to its dynamic power consumption. Embedded applications typically "idle" the CPU clock during periods of inactivity to reduce dynamic power consumption, significantly reducing overall power consumption. In the future design, special attention must be paid to the static power problem, because the leakage current of the new transistor with higher performance will be significantly improved.

Embedded system common technology

Commonly used power management techniques can be divided into two categories: when implemented through early hardware design decisions, or when the system is running. Early design decisions are critical to meeting performance and power consumption. The top ten factors that need to be considered in the design are listed below, including hardware selection, design strategy, and architecture choices. Most of the elements are basic requirements for embedded systems, while others need to be considered separately. Although the following decisions were made early in the design, some still need to be revalidated throughout the design cycle. As listed below:

1. Select a low power component;

2. Split voltage and clock domain;

3. Support voltage and frequency adjustment functions;

4. Enable the hold voltage gating function;

5. Reduce polling by software using interrupts;

6. Adopt a hierarchical memory model;

7. Reduce the output load;

8. Turn off power supply to non-critical resources when the system starts up;

9. Minimize the number of active PLLs;

10. Use the clock divider to quickly change the frequency.

Once the system architecture is determined, the design team needs to turn its attention to the system runtime environment. The 14 items listed below should always pay attention to most of them during the design process:

1. Turn off the gated clock when it is not needed;

2. Proactively turn off unnecessary power consumption during the boot process;

3. Supply power to the subsystem only when needed;

4. Activate the peripheral low power mode;

5. Make full use of the peripheral activity status detector;

6. Use the auto refresh mode;

7. Benchmark the application to determine the minimum frequency and voltage required;

8. Adjust the CPU frequency and voltage according to the overall activity;

9. Dynamically adjust the CPU frequency and voltage to match the expected workload;

10. Optimize the execution speed of the code;

11. Use low power code sequences and data patterns;

12. Use code coverage techniques to reduce the need for high-speed memory;

13. Enter the simplified function mode when replacing the power supply;

14. Balance accuracy versus power consumption.

Experienced design teams must be at least conceptually familiar with the above-mentioned embedded system application design points (some of which are related to DSP circuits). Any design that reduces power consumption can have a negative impact on performance or cause system instability.

How DSP RTOS meets low power design requirements

Some of the most important and generally accepted technical methods can be integrated into the RTOS. Related technologies include: idle, power off, device driver notification, memory management, voltage/frequency regulation. However, because the design goals are not the same, it is not easy to build these technologies into the RTOS. Designers need to choose between these methods. The key goals of the design are efficiency, flexibility, and loose relationship with the operating system itself.

TI's DSP/BIOS operating system Power Manager (PWRM) is ideally suited for use as a power management module for existing RTOS. Although the design implementation described below is for DSP/BIOS, the concept can be easily applied to other operating systems, even for operating environments without an operating system.

Our factory make the Stainless Steel Spool according to customer's drawing or samples.

ONEREEL stainless steel spools are highly resistant to chemical & salt water corrosion. They are popular for marine applications such as Refueling or wash down and are food grade for hygienic food preparation areas.

For customer service, call 0086-13777009159(mobile) or 0086-574-26889982(telephone)

Stainless Steel Spool

Stainless Steel Spool, Stainless Steel Wire Spool, Stainless Steel Reel, Stainless Steel Cable Spool

NINGBO BEILUN TIAOYUE MACHINE CO., LTD. , https://www.spool-manufacturer.com