Joel Cambonie, co-founder and vice president of engineering at GreenWaves, said GAP8 can achieve twice the energy efficiency of cores such as the ARM Cortex-M0 to Cortex-M7.

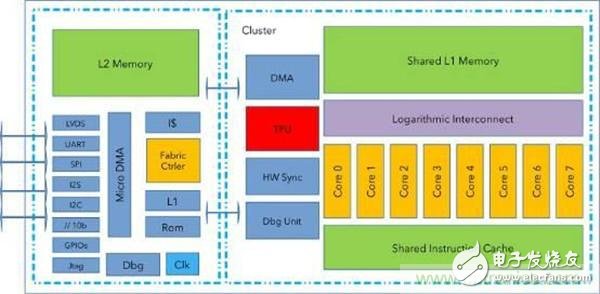

The GAP8 processor is derived from the RISC-V open source hardware PULP core technology transfer developed by the UniversiTIes of Bologna and the Swiss Federal Institute of Technology (ETF Zurich). The GAP8 uses eight PULP cores and one TensorFlow processor element (TPU) to accelerate the convolutional neural network for hardware-based pattern matching applications.

According to Cambonie, the processor can be programmed via C/C++/OpenMP and compiled with a standard GCC compiler with extended functionality.

The chip is planned to use TSMC's 55nm 55LP manufacturing process and is expected to be released in December this year. Cambonie said at the 2016 European Semiconductor Show (Semicon Europa) that the chip is expected to be released in February 2017. According to the simulation test results, the chip can achieve the original performance of 12GOPS. For sensor-type applications, the test bench shows 40MOPS performance at 400MOPS or 300mW at 1mW.

The GAP8 processor is expected to be used in applications such as image analysis, motion and vibration analysis, and speech recognition. It also acts as a soft modem platform and supports multiple IoT wireless communication solutions.

It supports standards such as 802.15.4g, LTE Cat-M and Cat-N1, and 802.11ah (WiFi HaLow). In addition to the GreenOFDM software implemented in GAP8, it is said that the power consumption of OFDM transmission can be reduced by an order of magnitude.

Ultra low power IoT processor GAP8 built-in 8 RISC-V cores and 1 Tensorflow accelerator

Extension: About RISC-V

The RISC-V instruction set architecture was originally developed by the University of California at Berkeley to help students learn about computer architecture, but now its creators want to push it to the mainstream to help drive emerging markets such as cloud computing and the Internet of Things.

David Patterson is one of the researchers behind RISC-V, the creator of the project, and the creator of the original RISC instruction set in the 1980s. He thinks this is a question about innovation. The popularity of the chip architecture has historically been locked up by major companies such as Intel, ARM and IBM (although IBM has opened up some OpenPower bases for industry partners) using strict licensing rules. He believes that even for companies that can afford the license fee, the instruction set they get may be complex and bloated, and it takes a lot of effort to produce the desired result.

Patterson said that many of today's processor architectures are actually based on RISC (including IBM Power, ARM, and MIPS), but these companies have benefited from what the patent system calls "quirks." These architectures are essentially the same, but technically different and require the operation of the instruction set. ARM - the company's design technology for Qualcomm, Apple, Marvell and other corporate smartphone chips and chips in Amazon and Google's data centers - is probably the most common example today.

Still, if you're a big company and can afford to buy licenses from big chip makers, it's good. These companies have spent a lot of money and time developing some very good technologies. But Patterson seems to be looking at the little guy outside the window—small companies or researchers want to develop their own chips for their specific applications, but they don't have much money. This requires the ability to experiment with the following instruction set, experiment with chip design and share your work publicly without fear of violating the license terms.

Patterso said, "To do this, you must have an unrestricted set of instructions."

In fact, there are other open source instruction sets, including OpenRISC and SPARC V8, as well as IBM's OpenPower and MIPS-based Prpl. It's still too early to talk about whether the latter can get, or get, the power – especially in small businesses, individual users and universities. Patterson said that the open source community has never really taken the path of OpenRISC and SPARC V8.

Patterson and his colleagues realized two years ago that they should try to promote RISC-V out of the classroom because people with "sufficient desperation and enough interest" asked if they could get it. At present, the University of California at Berkeley has created several cores based on RISC-V, and several other organizations have several projects underway.

Patterson said that RISC-V is more powerful and efficient in many ways (even compared to some proprietary designs) and is now an ideal moment because it has a small code base and other features that make it even more Suitable for chip system design, chip system design can dominate the computing world today mainly thanks to ARM. As the demand for connected devices evolves, with kits such as the Raspberry Pi becoming more mature and the growth of scale-out cloud computing architectures, a thriving RISC-V community should be able to design chips that will evolve with them.

Patterson responded to my question about how RISC-V fits into existing open source projects, such as the Open Compute Project created by Facebook. "We think it makes sense to design personalized hardware for cloud computing, it will be better than standard. The processor is more efficient.†He also said that the work done at the AMP Lab in the University of California at Berkeley is around data processing and distribution systems. He believes that a chip architecture that can be easily customized can also help solve fault tolerance problems. 64-bit addressing storage space may be an insufficient problem in some cases.

Patterson said, "I think this will happen." He said, "The hardware will be more targeted to customers and cloud computing."

Pressure Beams and circular plates on elastic foundations are considered. In some cases, additional elastic supports are present. The stiffness distribution of the foundation is designed so that the pressure on the foundation is uniform. Sometimes the depth of the beam or plate is also varied, with either a piecewise-constant sandwich or solid cross-section, and a global measure of the deflection is minimized. The total stiffness of the foundation and supports is specified, as well as the volume of the structure. In one type of problem, the edges of the structure are displaced downwards; in the other examples, a downward load is applied. Types of loads include a concentrated central load, a uniform load and a parabolic load. The uniform foundation pressure for the resulting design is often substantially lower than the maximum pressure for a corresponding uniform beam or plate on an elastic foundation with uniform stiffness.

Pressure Beams,Wood Wire Clips,Transformers Wood Wire Clips,Transformers Laminated Wood Wire Clips

Yingkou Dongyuan Electrical Insulation Board Co.,Ltd , https://www.dy-insulation.com